HBM thế hệ mới có thể dày hơn: Áp lực stack 20 lớp khiến ngành chip phải thay đổi tiêu chuẩn

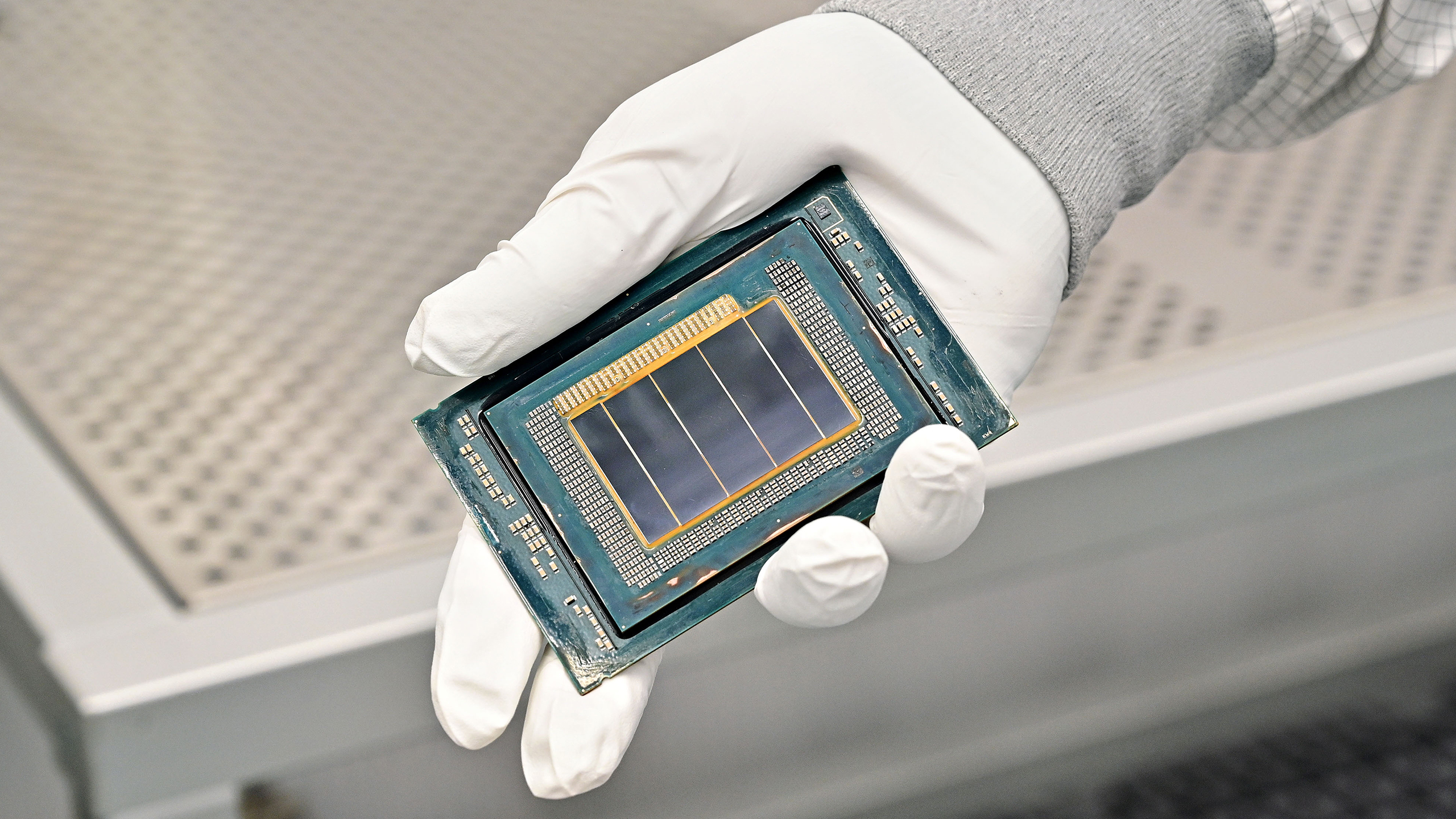

Các hãng bán dẫn đang cân nhắc nới lỏng tiêu chuẩn độ dày của bộ nhớ HBM cho các thế hệ tiếp theo. Nguyên nhân chủ yếu đến từ việc HBM4E và HBM5 dự kiến sử dụng cấu trúc xếp chồng tới 20 lớp chip, khiến việc giữ độ mỏng như trước ngày càng khó khăn.

Hiện nay, tiêu chuẩn độ dày của HBM4 là khoảng 775 micromet. Tuy nhiên, theo các thảo luận trong ngành, giới hạn này có thể được nâng lên khoảng 825-900 micromet cho các thế hệ HBM tiếp theo. Nếu vượt mốc 900 micromet, đây sẽ là mức tăng đáng kể so với các thế hệ trước.

Stack 20 lớp khiến việc giữ HBM mỏng trở nên khó hơn

Trong các thế hệ trước, độ dày của HBM được kiểm soát khá chặt chẽ. Từ HBM3E trở về trước, tiêu chuẩn chỉ khoảng 720 micromet. Khi sang HBM4, con số này đã tăng lên 775 micromet.

Tuy nhiên, khi các nhà sản xuất chuyển sang cấu trúc 20 lớp DRAM, việc tiếp tục giảm hoặc giữ nguyên độ dày trở nên rất khó về mặt kỹ thuật. Càng nhiều lớp chip được xếp chồng, tổng chiều cao của stack càng tăng, buộc ngành công nghiệp phải cân nhắc nới tiêu chuẩn.

Công nghệ đóng gói mới của TSMC cũng tác động tới tiêu chuẩn HBM

Một yếu tố khác ảnh hưởng tới các cuộc thảo luận là công nghệ đóng gói thế hệ mới. Khi các hãng sử dụng công nghệ SoIC của TSMC, độ dày của các chip hệ thống có thể tăng thêm vài chục micromet so với mức hiện tại.

Điều này khiến toàn bộ hệ thống đóng gói trở nên dày hơn, nên tiêu chuẩn độ dày của HBM cũng có thể phải điều chỉnh để phù hợp. Một số công ty lớn như NVIDIA và Amazon Web Services được cho là đang lên kế hoạch sử dụng công nghệ đóng gói này trong các hệ thống AI tương lai.

Việc nới tiêu chuẩn độ dày có thể làm chậm công nghệ hybrid bonding

Việc cho phép HBM dày hơn cũng có thể ảnh hưởng đến tốc độ triển khai một công nghệ quan trọng là hybrid bonding.

Hiện nay, các chip DRAM trong HBM thường được kết nối bằng phương pháp TC bonding, sử dụng nhiệt và lực nén. Trong khi đó, hybrid bonding là công nghệ tiên tiến hơn, cho phép kết nối trực tiếp các liên kết đồng giữa chip và wafer, giúp giảm khoảng cách giữa các lớp DRAM gần như về 0 và làm cho toàn bộ stack mỏng hơn.

Tuy nhiên, hybrid bonding rất khó triển khai trong sản xuất hàng loạt. Công nghệ này yêu cầu bề mặt cực kỳ sạch, độ chính xác căn chỉnh rất cao, và tỷ lệ thành phẩm có thể giảm khi phải kết nối tới 20 lớp chip.

Vì vậy, dù các hãng bộ nhớ lớn vẫn tiếp tục đầu tư nghiên cứu, hybrid bonding vẫn chưa được sử dụng rộng rãi trong sản xuất HBM. Ngay cả Samsung, một trong những công ty tích cực phát triển công nghệ này, cũng chỉ dự kiến áp dụng một phần trong các sản phẩm HBM4E 16 lớp sớm nhất.

Chia sẻ bài viết

Bình luận

( 0 bình luận )Bình luận của bạn

Tin tức liên quan